基于FPGA器件实现多频键控调制电路的设计和仿真验证研究

数字信号传输系统分为基带传输系统和频带传输系统.频带传输系统也叫数字调制系统。数字调制信号又称为键控信号,数字调制过程中处理的是数字信号,而载波有振幅、频率和相位3个变量,且二进制的信号只有高低电平两个逻辑量1和0,所以调制的过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制,最基本的方法有3种:正交幅度调制(QAM)、频移键控(FSK)、相移键控(PSK).根据所处理的基带信号的进制不同分为二进制和多进制调制(M 进制).多进制数字调制与二进制相比,其频谱利用率更高。本文研究了基于FPGA的MFSK(多频键控)调制电路的实现方法,并给出了MAX+PLUSII环境下的仿真结果。

1、 MFSK简介

MFSK系统是2FSK(二频键控)系统的推广,该系统有M个不同的载波频率可供选择,每一个载波频率对应一个M进制码元信息,即用多个频率不同的正弦波分别代表不同的数字信号,在某一码元时间内只发送其中一个频率。MFSK信号可表示为:

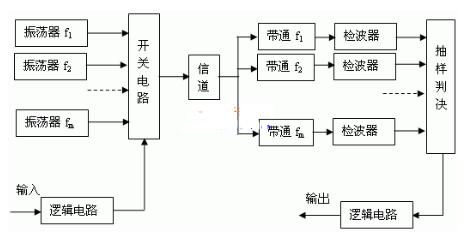

为载波角频率,通常采用相位不连续的振荡频率,这样便于利用合成器来提供稳定的信号频率。图1 为MFSK系统的原理框图。在发送端,输入的二进制码元经过逻辑电路和串/并变换电路转换为M进制码元,每k位二进制码分为一组,用来选择不同的发送频率。在接收端,当某一载波频率到来时,只有相应频率的带通滤波器能收到信号,其它带通滤波器输出的都是噪声。抽样判决器的任务就是在某一时刻比较所有包络检波器的输出电压,通过选择最大值来进行判决。将最大值输出就得到一个M进制码元,然后,再经过逻辑电路转换成k位二进制并行码,再经过并/串变换电路转换成串行二进制码,从而完成解调过程。

图1 MFSK系统原理框图

2、 MFSK调制电路的FPGA实现

2.1 基于FPGA的MFSK调制电路方框图

调制电路方框图如图2所示。基带信号通过串/并转换得到2位并行信号;四选一开关根据两位并行信号选择相应的载波输出(例中M取4)。

图2 MFSK调制电路方框图

2.2 MFSK调制电路VHDL程序

调制电路VHDL关键代码如下:

entity MFSK is

port(clk :in std_logic; --系统时钟

start :in std_logic; --开始调制信号

x :in std_logic; --基带信号

y ut std_logic); --调制信号

end MFSK;

architecture behav of MFSK is

signal q :integer range 0 to 15; --计数器

signal f :std_logic_vector(3 downto 0); --分频器

signal xx:std_logic_vector(1 downto 0); --寄存输入信号x的2位寄存器

signal yy:std_logic_vector(1 downto 0); --寄存xx信号的寄存器

begin

process(clk) --此进程过对clk进行分频,得到4种载波信号f3、f2、 f1、f0。

begin

if clk‘event and clk=’1‘ then

if start=’0‘ then f elsif f=“1111” then f else f end if;

end if;

end process;

process(clk) --对输入的基带信号x进行串/并转换,得到2位并行信号的yy

begin

if clk’event and clk=‘1’ then

if start=‘0’ then q elsif q=0 then q elsif q=8 then q else q end if;

end if;

end process;

process(clk,yy) --此进程完成对输入基带信号x的MFSK调制

begin

if clk‘event and clk=’1‘ then

if start=’0‘ then y elsif yy=“00” then y elsif yy=“01” then y elsif yy=“10” then y else y end if;

end if;

end process;

end behav;

2.3 仿真结果

MAX+PLUSII环境下的仿真结果如图3所示。

图3 MFSK调制程序仿真结果

注:中间信号yy与输出调制信号y的对应关系:“00”=f3;“01”=f2;“10”=f1;“11”=f0。

3、 结束语

多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。本文基于FPGA实现了MFSK调制电路部分,限于篇幅,没有对解调部分的电路进行讨论。在实际应用中,完全可以把调制部分和解调部分电路都集成到一片FPGA芯片内,这样即提高了FPGA内部结构的利用率,又可以降低系统的成本。容-源-电-子-网-为你提供技术支持

本文地址:http://www.dziuu.com/dz/22/15954969563916.shtml

本文标签:

- 上一篇文章:新手教程:单片机的学习实践步骤

- 下一篇文章:可满足各种测试环境要求的多路信号源的设计

-

学习单片机可不可以只用软件仿真而不做实验

学习单片机可不可以只用软件仿真而不做实验

我的答案是:不可以原因如下:一、软件仿真多用于教学,把更多精力用在软件的实现上由于学生学习时间宝贵,焊接一套单片机实验板又比较花时间,并且实验项目太多,所以为了

关键词:PIC单片机51单片机单片机 所属栏目:设计编程 -

超详细的FPGA芯片解读(图文)

超详细的FPGA芯片解读(图文)

近日,有媒体报道称,北京微电子技术研究所日前成功研制出国内首个自主可控的宇航用千万门级高性能高可靠FPGA(现场可编程门阵列)芯片。FPGA一直是国内的短板,市场基本被

关键词:单片机 所属栏目:设计编程 -

基于FPGA的32位嵌入式处理器的解决方案

基于FPGA的32位嵌入式处理器的解决方案

嵌入式系统与桌面PC结构非常不同,但其底层技术发展却是一样的,而且遵循着类似发展趋势。当桌面PC转向64位架构来满足不断增长的存储器要求时,嵌入式系统也由于同样的原因

关键词: 所属栏目:设计编程 -

800W双向可控调光器电路

800W双向可控调光器电路

无

关键词: 所属栏目:电子制作 -

转:大功率时控调压的实现

转:大功率时控调压的实现

无

关键词: 所属栏目:电源电路 -

介绍常用EDA设计与仿真软件

介绍常用EDA设计与仿真软件

无

关键词: 所属栏目:电子基础 -

高压变频器单元热仿真计算

高压变频器单元热仿真计算

-

multisim的使用方法及中英文对照表

multisim的使用方法及中英文对照表

无

关键词: 所属栏目:设计编程 -

提供multisim8 multisim9 multisim 2001的序列号

提供multisim8 multisim9 multisim 2001的序列号

无

关键词: 所属栏目:设计编程 -

电子仿真软件EWB中英文对照表

电子仿真软件EWB中英文对照表

无

关键词: 所属栏目:其他文章

猜你感兴趣:

- 最新内容

-

- 无源晶振选型 2024-10-10

- ACM6755 支持3霍尔应用的全集成三相直流无刷电机驱动IC方案 2024-10-09

- YXC晶振解决方案助力工业相机应用 2024-09-27

- 有源晶振和无源晶振的区别 2024-09-24

- 光模块热度不减,最佳时频CP-差分晶振 2024-09-20

- 晶体谐振器的工作原理 2024-09-19

- YXC石英有源差分可编程晶振,频点200MHZ,小数点可精确至后6位,应用于5G基站 2024-09-12

- 70V耐压可调OVP阈值的过压保护芯-平芯微PW1600 2024-09-05

- YXC扬兴有源新品发布丨1.2V超低功耗时钟解决方案 2024-09-05

- YXC扬兴 | 32.768KHZ晶振选型分享 2024-09-02

- 热门标签

-